[HARMAN 세미콘]Full custom IC one chip 설계 1일차

1. 디지털 - 노이즈 영향이 거의 없음

2. 아날로그 - 노이즈에 critical 한 영향을 받음

3. CMOS란 : Complementary metal-oxide-semiconductor

4. 집적률이 높아지면 -> 스위칭 속도 감소, supply voltage 감소, power 소모 감소

집적률이 더 이상 높아져도 배터리 문제가 해결되지 않으면 아무리 집적률이 높아져도 의미 없음

5. 낮은 공정일 수록 아날로그적으로 noise 문제가 발생하여 아날로그는 대부분 조금 큰 집적도의 회로를 사용함

netlist: 회로 합성 후 나오는 결과

wapper에 pad가 ESD , Noise방지 역할을 하게 된다.

비동기식으로 설계를 하게되면 레이싱 현상이 발생할 수 있다.

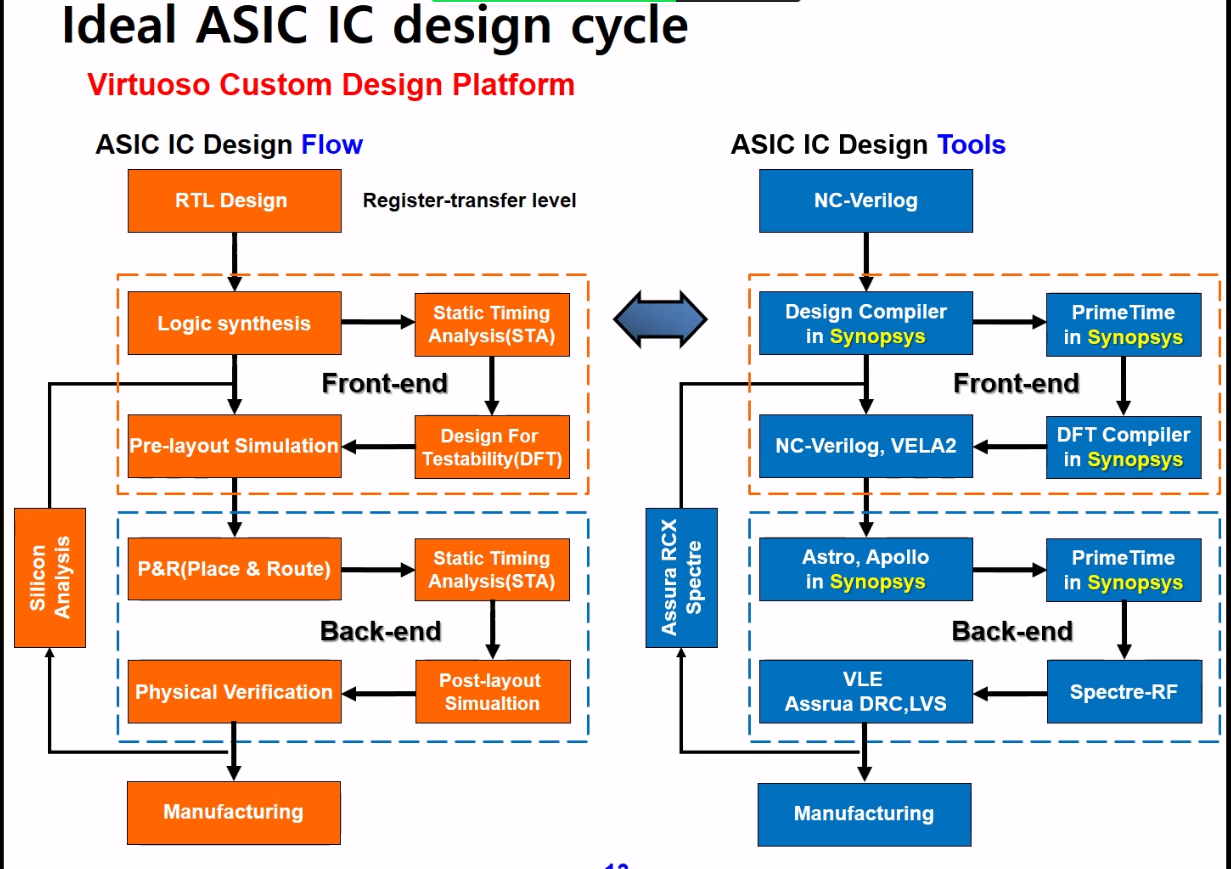

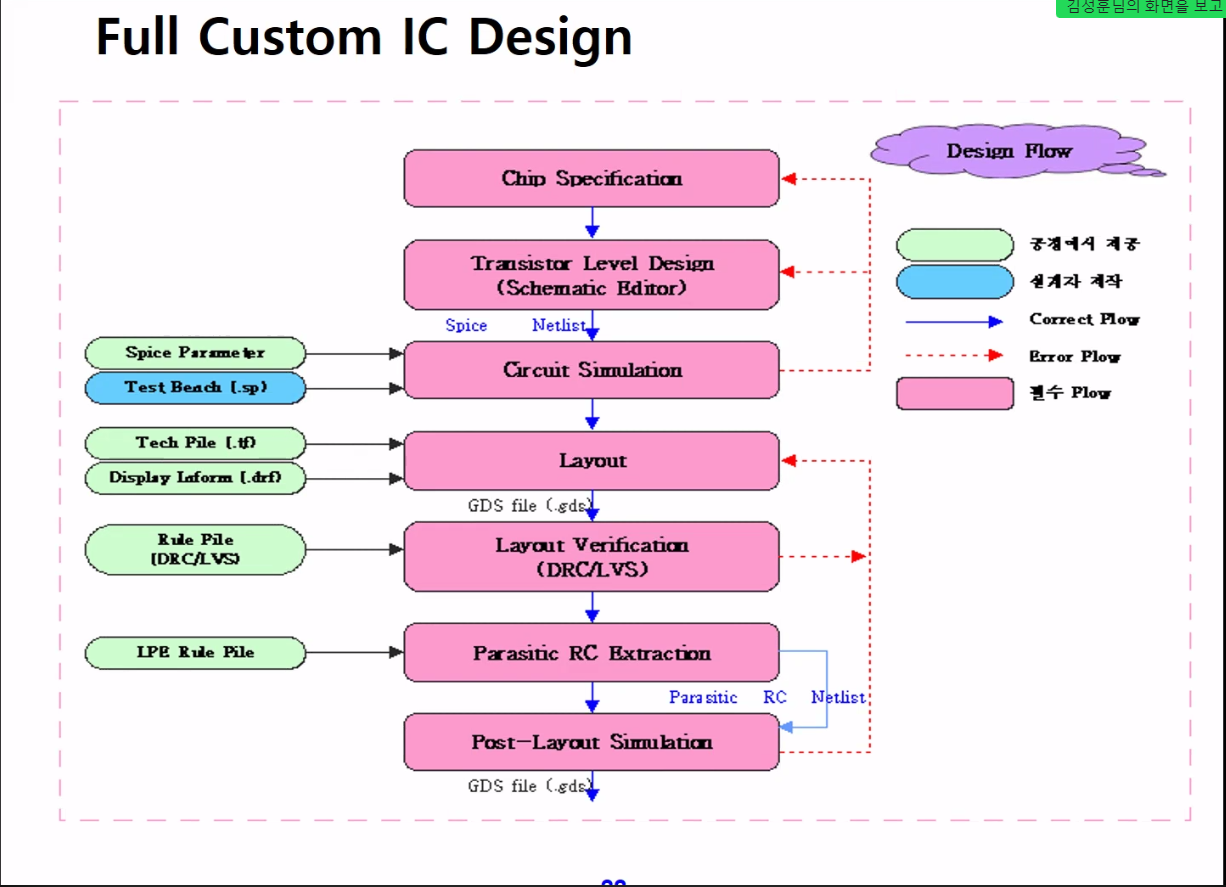

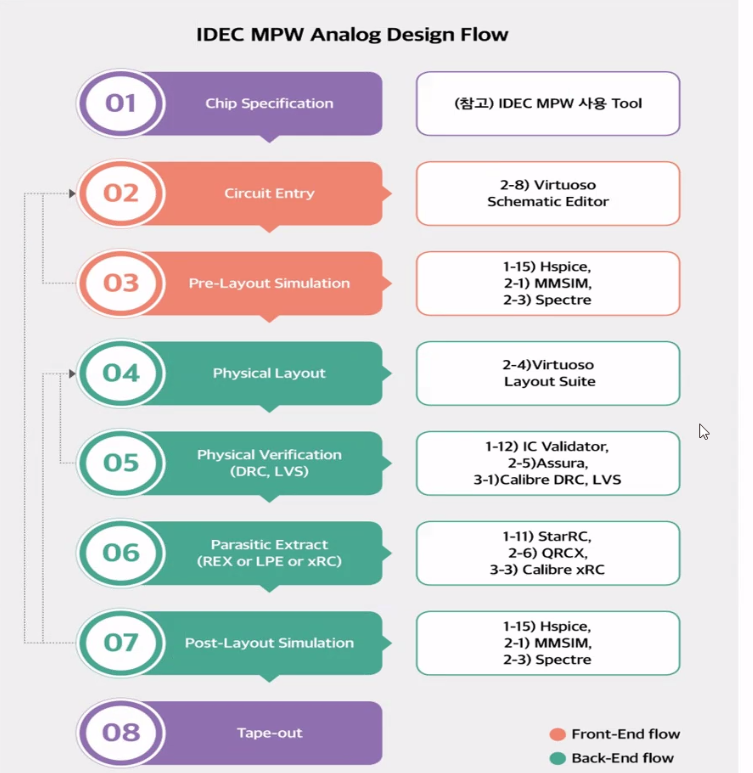

full custom 디자인 전체 flow

1. chip specification : 칩 스펙을 먼저 정의한다.

2. Transistor Level Design : 사용자의 요구에 맞춰서 어떠한 Transistor를 사용해서 설계할 것인지에 대한 level

BJT와 MOSFET의 차이

3. circuit simulation : spice 툴을 사용한 회로 검증 및 시뮬레이션 과정

/// 여기까지가 front-end 과정 spec이 맞을 때까지 계속해서 반복하게 됨

////여기서부터는 back-end과정

4. Layout : PDK 파일을 기준으로 Layout 설계

5. Layout verification : Design rule check를 하게 됨

6. parasitic RC extraction: 기생성분을 추출하는 과정(resister, capacitance)

7. post - layout simulation : 기생성분이 있는 layout을 그리는 과정

자주 사용하는 리눅스 명령어

TAR(Tape ARchive) 명령어: 파일 및 디렉터리를 아카이브로 묶는 명령어

Gzip 명령어 : 파일 및 디렉터리를 압축하는 명령어

( gzip -d: 압축 해제)

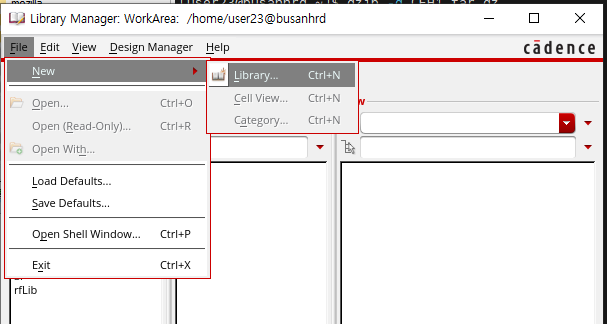

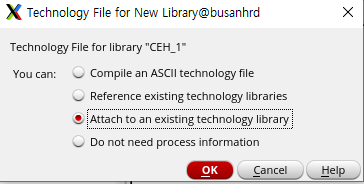

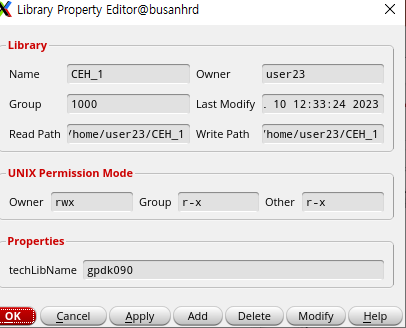

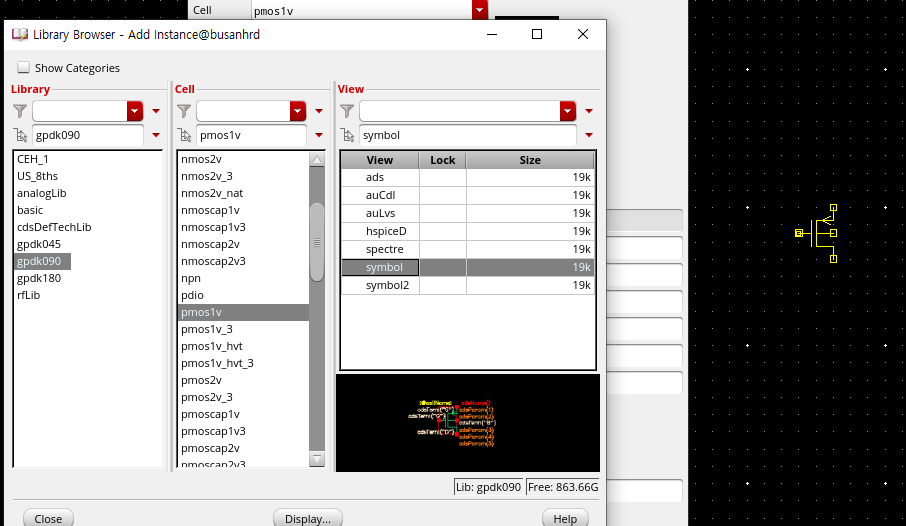

vertuoso library 생성 :

library manager 선택

new -> library 선택

attach to an ~~ 선택

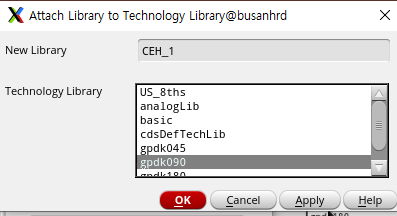

공정회사에서 제공해 주는 90n 파일 선택

해당 파일에서 layout이나 symbol 등이 나와있다.

properties 선택 후 gPDK파일이 90n가 선택되어 있는지 확인.

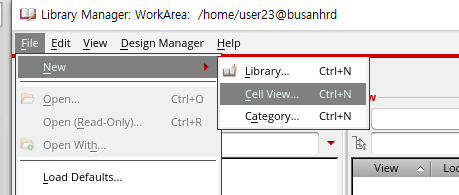

cell 이름 설정

이렇게 layout을 그릴 수 있는 schematic이 나타나게 됨.

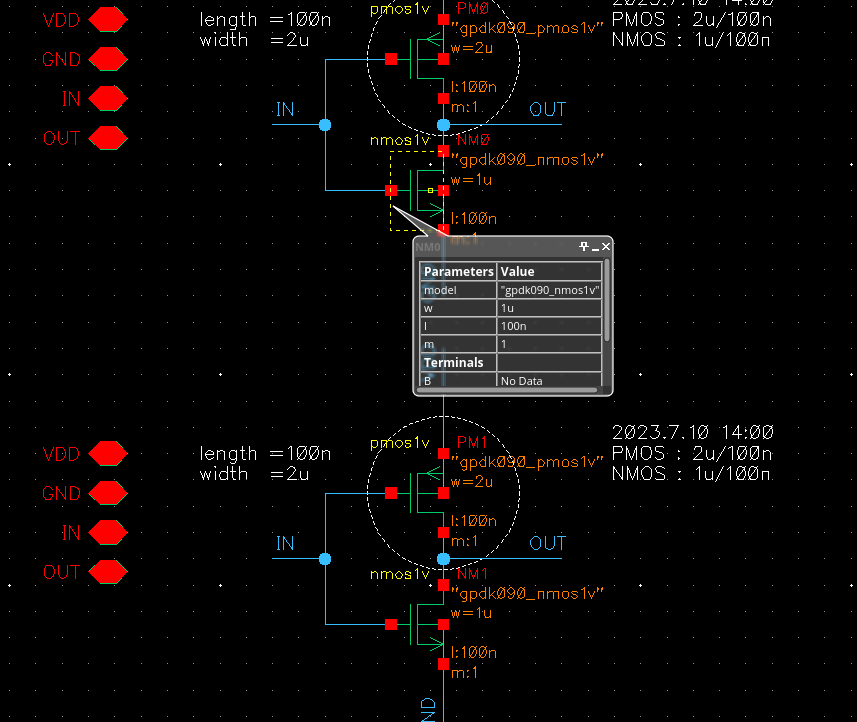

instance 선택

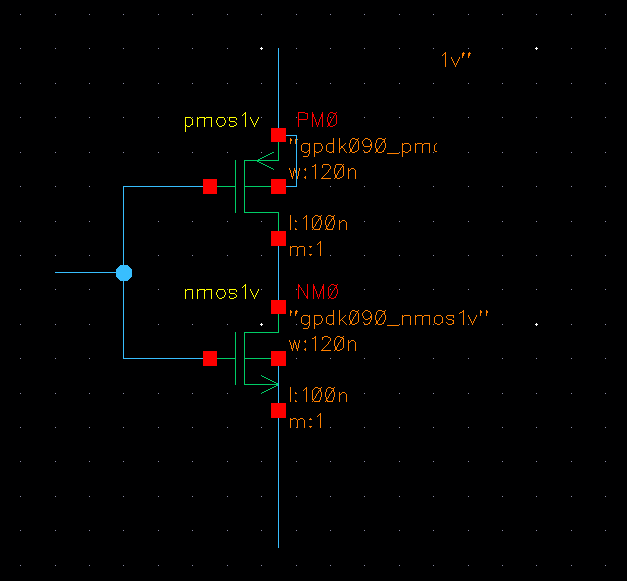

부품 배치 후 선 연결(analog에서는 narrow타입을 주로 씀)

각 WIRE의 이름을 정해준다

그리고 PIN을 설정해 준다

보통 출력선이 다시 입력선이 되는 경우를 대비해서 DIRECTION을 INPUT OUTPUT으로 설정해 준다

\

Check and save: 회로의 문제를 확인하기 위해 이걸 클릭한다.

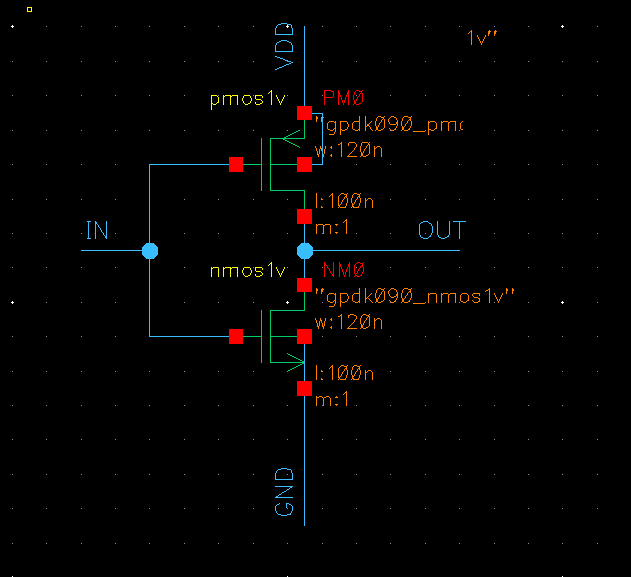

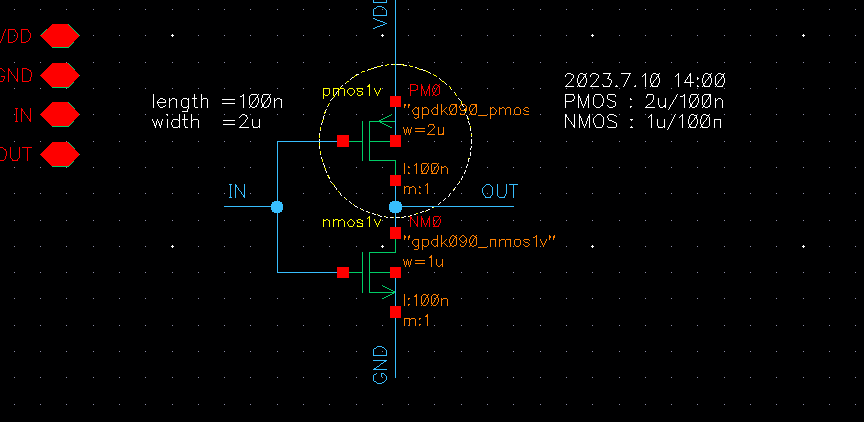

위의 회로는 PMOS, NMOS의 이동도 차이 때문에 정상적으로 동작하지 않는다

이러한 차이를 없애기 위해 WIDTH랑 LENGTH를 조절해줘야 한다

Fingers를 조절하여 병렬 구조를 simple하게 만들 수 있음

parameter들이 변경된 후

note -> shape를 통해 주석을 달 수 있다.

Net Highlighting을 선택하면 해당 회로가 어디랑 연결되어 있는지 확인할 수 있음

info balloons를 선택하면

이렇게 소자들의 특성을 확인할 수 있다.

Display Dimming을 선택하면

이렇게 소자에 highlight가 적용된다.

복사를 하면서 f3번을 누르면 여러 개 복사가 가능하다

이렇게 다양한 명령어들을 이용하여 schematic을 설게 할 수 있다

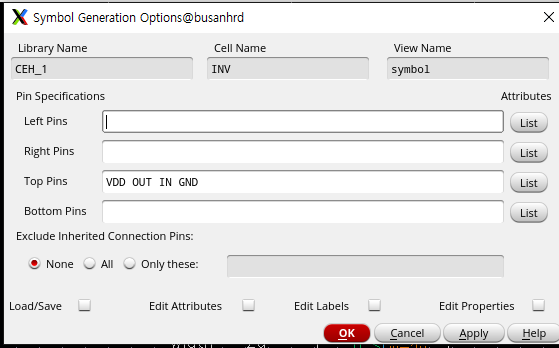

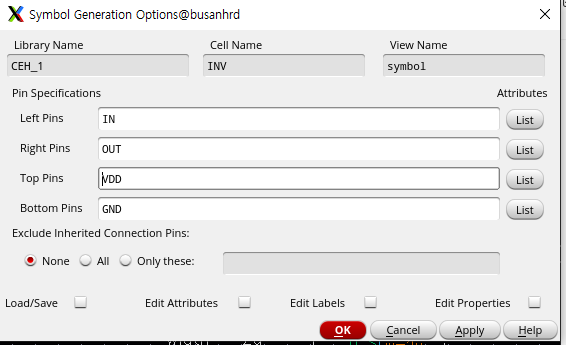

이렇게 설계된 schematic의 symbol을 설계해 보자

left pin, right pins, top, bottom pin을 설정해 준다.(왼쪽 in, 오른쪽 out, 위쪽 vdd, 아래쪽 gnd)

이렇게 핀 설정을 하면 symbol을 그리는 화면이 나온다

이러한 simbol을 create line 등을 사용하여 다시 그린다

이렇게 만들고 check and save를 선택하고 그냥 나가면 된다.

이렇게 생성된 symbol을 확인해 보자

새롭게 파일을 연 후 instance를 하게 되면

이렇게 우리가 제작한 symbol들을 사용할 수 있다.

이 symbol의 내부 회로를 확인하고자 하면 symbol 클릭 후 dessend edit를 선택하면 된다.

이렇게 내부 회로를 확인할 수 있다.

여기서 ctrl + e를 누르면 다시 symbol을 확인할 수 있다.

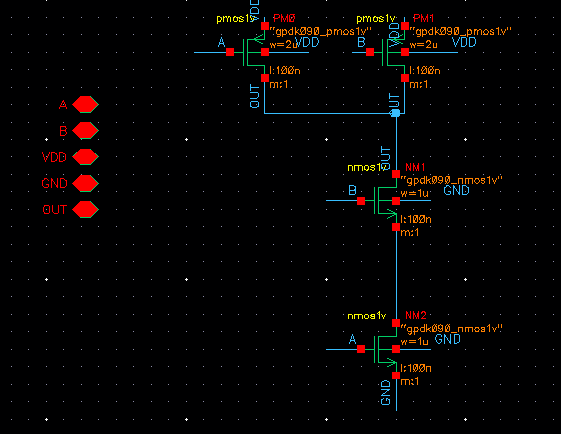

NAND 설계

instance를 하고 난 후 all terminals를 선택하고... 을 선택하면

각 핀의 이름과 net name을 설정할 수 있다.

이렇게 wire name이 지정되는 것을 확인할 수 있다.

이렇게 NAND를 설계해보면

이렇게 PMOS 병렬, NMOS 직렬 형태로 설계할 수 있다. 이러한 NAND게이트의 심벌을 제작하였다

SHIFT + E버튼을 통해 NAND게이트의 내부 구조를 확인할 수 있다.

이러한 동일한 방법으로 NOR게이트를 설계해 보자